## TMP8155P-2/TMP8156P-2

## 256 BYTE STATIC RAM WITH I/O PORTS AND TIMER

## 1. GENERAL DESCRIPTION

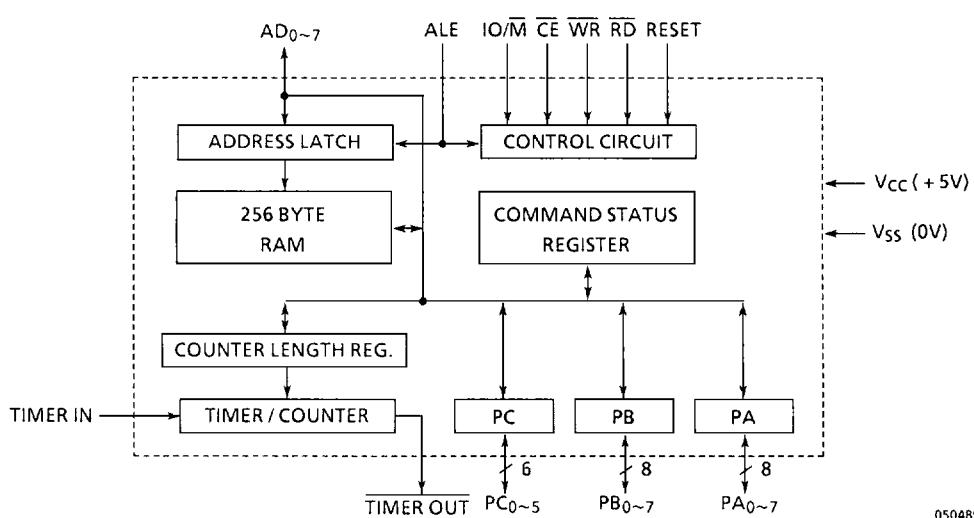

The TMP8155/8156P-2 are RAM including I/O ports and counter/timer on one chip for using in the TLCS-85A microcomputer system. The RAM portion is designed with 2K bit static memory cells organized as 256 x 8. The 14 bit programmable counter/timer is the down counter. It provides either a square wave terminal count pulse for the MPU system depending on timer mode.

The I/O portion consists of 2 programmable 8 bit I/O ports and 1 programmable 6 bit I/O port. The programmable I/O ports can be operated by BASIC MODE and STROBE MODE.

## 2. FEATURES

- Single +5V Power supply

- Access Time: 330 ns

- Internal Address Latch

- 2 Programmable 8 bit I/O Ports and 1 Programmable 6 bit I/O Port

- 256 x 8 bit RAM

- Programmable 14 bit Binary Counter/Timer

- Multiplexed Address/Data Bus

- Chip Enable Active High (TMP8156P-2) or Low (TMP8155P-2)

- 40 pin DIP

## 3. PIN CONNECTION (TOP VIEW)

|                         |    |    |                 |

|-------------------------|----|----|-----------------|

| PC <sub>3</sub>         | 1  | 40 | V <sub>CC</sub> |

| PC <sub>4</sub>         | 2  | 39 | PC <sub>2</sub> |

| TIMER IN                | 3  | 38 | PC <sub>1</sub> |

| RESET                   | 4  | 37 | PC <sub>0</sub> |

| PC <sub>5</sub>         | 5  | 36 | PB <sub>7</sub> |

| TIMEROUT                | 6  | 35 | PB <sub>6</sub> |

| IO/M                    | 7  | 34 | PB <sub>5</sub> |

| * CE OR $\overline{CE}$ | 8  | 33 | PB <sub>4</sub> |

| RD                      | 9  | 32 | PB <sub>3</sub> |

| WR                      | 10 | 31 | PB <sub>2</sub> |

| ALE                     | 11 | 30 | PB <sub>1</sub> |

| AD <sub>0</sub>         | 12 | 29 | PB <sub>0</sub> |

| AD <sub>1</sub>         | 13 | 28 | PA <sub>7</sub> |

| AD <sub>2</sub>         | 14 | 27 | PA <sub>6</sub> |

| AD <sub>3</sub>         | 15 | 26 | PA <sub>5</sub> |

| AD <sub>4</sub>         | 16 | 25 | PA <sub>4</sub> |

| AD <sub>5</sub>         | 17 | 24 | PA <sub>3</sub> |

| AD <sub>6</sub>         | 18 | 23 | PA <sub>2</sub> |

| AD <sub>7</sub>         | 19 | 22 | PA <sub>1</sub> |

| V <sub>SS</sub>         | 20 | 21 | PA <sub>0</sub> |

050489

Figure 3.1

Note: \* TMP8155 =  $\overline{CE}$

TMP8156 = CE

## 4. BLOCK DIAGRAM

050489

Figure 4.1

## 5. PIN NAMES AND PIN DESCRIPTION

- **RESET (INPUT)**

The Reset signal is a pulse provided by TMP8085A to initialize the system. Input high on this line resets the chip and initializes the internal three I/O ports to input mode.

The width of RESET pulse should typically be two clock cycles of TMP8085A.

- **AD<sub>0~7</sub> (INPUT/OUTPUT, 3-STATE)**

These are 3-state Address/Data lines that interface with the MPU lower 8-bit Address/Data Bus. The 8-bit address can be applied to the memory section or the I/O section depending on the polarity of the IO/M input signal. 8-bit data is either written into or read from the TMP8155/8156 depending on the status of WR or RD input signal.

- **CE OR  $\overline{CE}$  (INPUT)**

Chip Enable : On the TMP8155P-2, this pin is  $\overline{CE}$  and is Active Low.

On The TMP8156P-2, this pin is CE and is Active High.

- **$\overline{RD}$  (INPUT)**

Input low on this line with the Chip Enable active enables the AD<sub>0~7</sub> buffers. If IO/M pin is low, the RAM content will be read out from the AD<sub>0~7</sub> bus. Otherwise the content of the selected I/O port or command/status register will be read out from the AD<sub>0~7</sub> bus.

- **$\overline{WR}$  (INPUT)**

Input low on this line with the active CE/ $\overline{CE}$  causes the data on the AD<sub>0~7</sub> lines to be written to the RAM or I/O ports and command/status register depending on the polarity of IO/M.

- **ALE (INPUT)**

Address Latch Enable : This control signal latches both the data on the AD<sub>0~7</sub> lines and the state of the Chip Enable and IO/M into the chip at the falling edge of ALE.

- **IO/M (INPUT)**

IO/Memory Select : This line selects the memory if low and selects the I/O or command/status register if high.

- **PA<sub>0~7</sub> (INPUT/OUTPUT, 3-STATE)**

These 8 pins are general purpose I/O pins. The in/out direction is selected by programming the Command Register.

- **PB<sub>0~7</sub> (INPUT/OUTPUT, 3-STATE)**

These 8 pins are general purpose I/O pins. The in/out direction is selected by programming the Command Register.

- **PC<sub>0~5</sub> (INPUT/OUTPUT, 3-STATE)**

These 6 pins can function as either input port, output port, or as control signal for PA and PB. Programming is done through the Command Register.

When PC<sub>0~5</sub> are used as control signals, they are defined as the following :

- PC0 - A INTR (Port A Interrupt)

- PC1 - A BF (Port A Buffer Full)

- PC2 - A STB (Port A Strobe)

- PC3 - B INTR (Port B Interrupt)

- PC4 - B BF (Port B Buffer Full)

- PC5 - B STB (Port B Strobe)

- **TIMER IN (INPUT)**

This is the input to the counter-timer.

- **TIMEROUT (OUTPUT)**

This pin is the timer output. This output can be either a square wave or a pulse depending on the timer mode.

- **VCC (Power)**

+ 5 volt supply

- **VSS (Power)**

Ground Reference

## 6. FUNCTIONAL DESCRIPTION

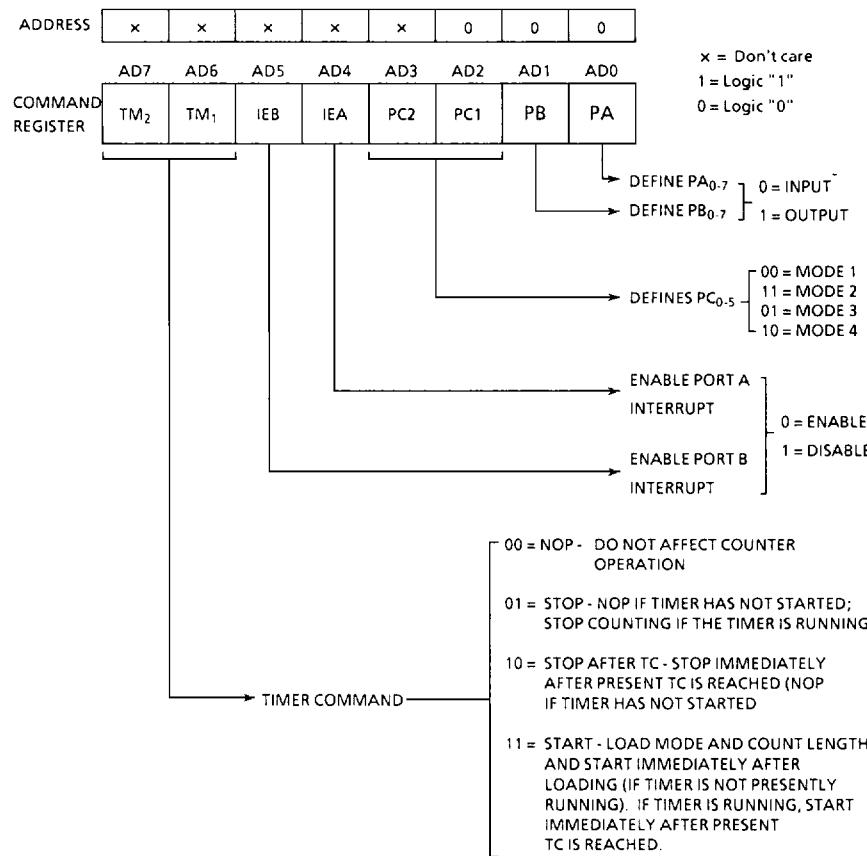

### 6.1 PROGRAMMING THE COMMAND REGISTER

The command register consists of either latches. Four bits (0-3) define the mode of the ports, two bits (4-5) enable or disable the interrupt from port C when it acts as control port, and the last two bits (6-7) are for the timer.

The command register contents can be altered at any time by using the I/O address XXXX000 during a WRITE operation. The functions of each bit of the command register is shown in Figure 6.1

Note that the command register is a write-only register and can not be read.

Figure 6.1 Command Register Bit Assignment

050489

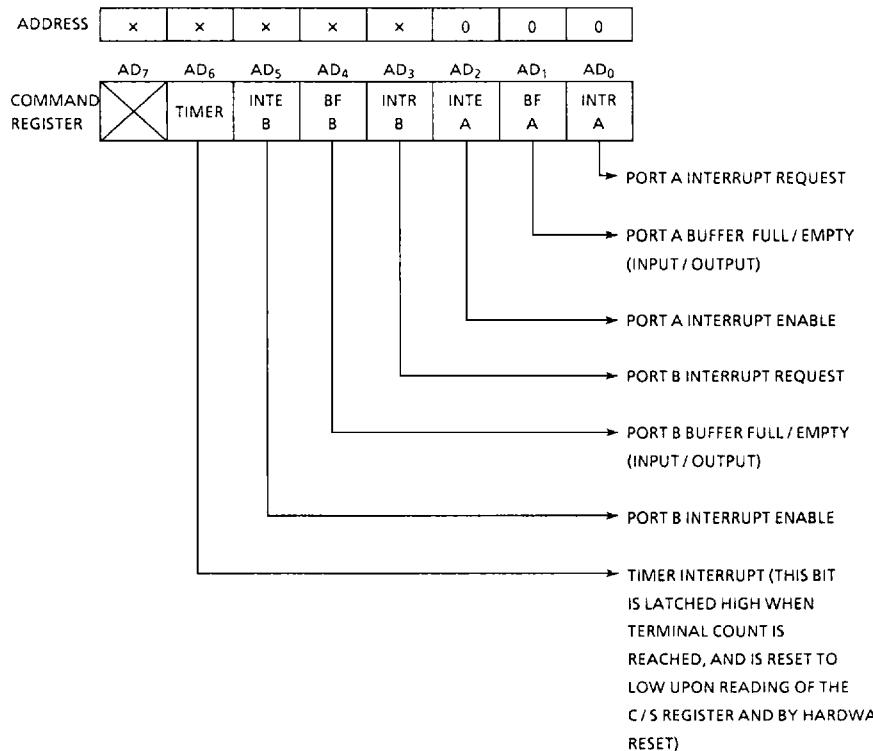

## 6.2 READING THE STATUS REGISTER

The status register consists of seven latches, one for each bit ; six (0-5) for the status of the ports and one (6) for the status of the timer.

The status of the timer and the I/O section can be polled by reading the Status Register (Address XXXX000). Status word format is shown in Figure 6.2.

050489

Figure 6.2 Status Register Bit Assignment

### 6.3 I/O SECTION

- **COMMAND/STATUS REGISTER (C/S)** – Both registers have the same address XXXXX000. When the C/S registers are selected during WRITE operation, a command is written into the C/S Register. The contents of this register are not accessible through the pins. When the C/S is selected during a READ operation, the status information of the I/O ports and the timer becomes available on the AD<sub>0~7</sub> lines.

- **PA Register** – This register can be programmed to be either input or output ports depending on the status of the contents of the C/S Register. Also depending on the command, this port can operate in either the basic mode or the strobed mode (See timing diagram). The I/O pins assigned in relation to this register are PA<sub>0~7</sub>. The address of this register is XXXXX001.

- **PB Register** – This register functions the same as PA Register. The I/O pins assigned are PB<sub>0~7</sub>. The address of this register is XXXXX010.

- **PC Register** – This register has the address XXXXX011 and contains only 6-bits. The 6-bits can be programmed to be either input ports, output ports or as control signals for PA and PB by properly programming the AD<sub>2</sub> and AD<sub>3</sub> bits of the C/S Register. When PC<sub>0~5</sub> is used as a control port, 3-bits are assigned for Port A and 3 for Port B. The first bit is an interrupt that the TMP8155/8156 issues. The second is an output signal indicating whether the buffer is full or empty, and the third is an input pin to accept a strobe for the strobed input mode. See Table 6.2. When the port C is programmed to either MODE 3 or MODE 4, the control signals for PA and PB are initialized as follows :

| CONTROL MODE | BF  | INTR | STB           |

|--------------|-----|------|---------------|

| INPUT MODE   | Low | Low  | Input Control |

| OUTPUT MODE  | Low | High | Input Control |

050489

To summarize, the register's address assignments are shown in Table 6.1.

Table 6.1 I/O Port Addressing Scheme

| I/O ADDRESS    |                |                |                |                |                |                |                | SELECTION         | NO. OF BITS                         |   |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------------------|-------------------------------------|---|

| A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                   |                                     |   |

| X              | X              | X              | X              | X              | 0              | 0              | 0              | Internal          | Command / Status Register           | 8 |

| X              | X              | X              | X              | X              | 0              | 0              | 1              | PA <sub>0-7</sub> | General Purpose I/O Port A          | 8 |

| X              | X              | X              | X              | X              | 0              | 1              | 0              | PB <sub>0-7</sub> | General Purpose I/O Port B          | 8 |

| X              | X              | X              | X              | X              | 0              | 1              | 1              | PC <sub>0-7</sub> | General Purpose I/O Port or Control | 6 |

| X              | X              | X              | X              | X              | 1              | 0              | 0              |                   | Low-Order 8 bits of Timer Count     |   |

| X              | X              | X              | X              | X              | 1              | 0              | 1              |                   | High 6 bits / 2 bits of Timer Count |   |

050489

Table 6.2 Port Control Assignment

| Pin | MODE 1     | MODE 2      | MODE 3                             | MODE 4                             |

|-----|------------|-------------|------------------------------------|------------------------------------|

| PC0 | Input Port | Output Port | A INTR (Port A Interrupt)          | A INTR (Port A Interrupt)          |

| PC1 | Input Port | Output Port | A BF (Port A Buffer Full)          | A BF (Port A Buffer Full)          |

| PC2 | Input Port | Output Port | A $\overline{STB}$ (Port A strobe) | A $\overline{STB}$ (Port A strobe) |

| PC3 | Input Port | Output Port | Output Port                        | B INTR (Port B Interrupt)          |

| PC4 | Input Port | Output Port | Output Port                        | B BF (Port B Buffer Full)          |

| PC5 | Input Port | Output Port | Output Port                        | B $\overline{STB}$ (Port B strobe) |

050489

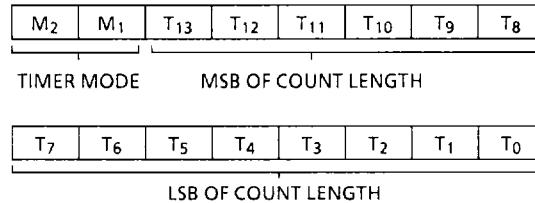

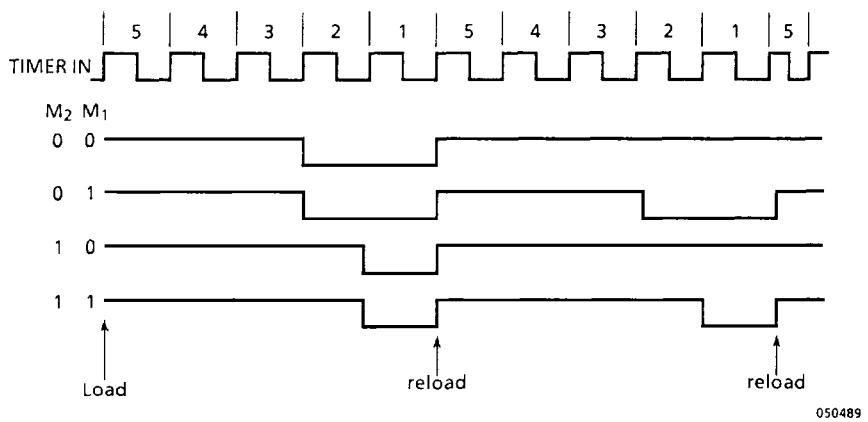

#### 6.4 TIMER SECTION

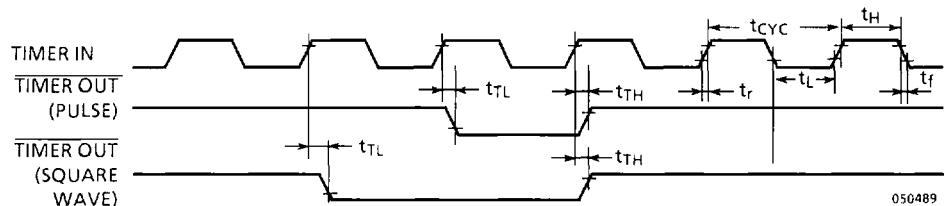

The timer is a 14-bit down-counter that counts the 'timer input' pulses and provides either a square wave or pulse when terminal count (TC) is reached.

The timer has I/O address XXXXX100 for the low order byte of the register and the I/O address XXXXX101 for the high order of the register.

To program the timer, the COUNT LENGTH REGISTER is loaded first, one byte at a time, by selecting the timer addresses. Bits 0-13 will specify the length of the next count and bits 14-15 will specify the timer output mode. The value loaded into the count length register can have any value from 2H through 3FFFH in bits 0-13.

050489

Figure 6.3 Timer Format

There are four timer modes which are defined by M2 and M1.

##### M2 M1

- 0 0 —— Put out low during second half of count.

- 0 1 —— Continuous square wave; The period of the square-wave equals the count length programmed with automatic reload at terminal count.

- 1 0 —— Single pulse upon TC being reached.

- 1 1 —— Continuous pulses.

Note: In case of an odd-numbered count, the first half-cycle of the square-wave output, which is high, is one count longer than the second (low) half-cycle as shown in Figure 6.3.

Figure 6.3 Asymmetrical Square-Wave Output resulting from Count 5

Bits 6-7 (TM2 and TM1) of command register contents are used to start and stop the counter. There are four commands to choose from;

TM2 TM1

|     |                                                                                                                                                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 | NOP : Do not affect counter operation.                                                                                                                                                                           |

| 0 1 | STOP : NOP if timer has not started; stop counting if the timer is running.                                                                                                                                      |

| 1 0 | STOP AFTER TC : Stop immediately after present TC is reached.<br>(NOP if timer has not started)                                                                                                                  |

| 1 1 | START : Load mode and count length and start immediately after loading (if timer is not presently running).<br>If timer is running, start the new mode and count length immediately after present TC is reached. |

Note that while the counter is counting, a new count and mode can be loaded into the count length registers. Before the new count and mode will be used by the counter, a START command should be issued to the counter. This applies even though only the change of the count is required in the previous (same) mode.

The counter in the TMP8155/8156 is not initialized to any particular mode or count when hardware RESET occurs, but RESET does stop the counting.

Therefore a START command must be issued via the C/S register, because counting cannot begin following RESET.

Note that the timer circuit on the TMP8155/8156 chip is designed to be a square-wave timer, not an event counter. To achieve this, it counts down by two twice in completing one cycle. Thus, its registers do not contain values directly representing the number of TIMER IN pulses received. Counter value '1' can't be loaded as the initial value into the count register because the timer operates as its terminal count value is 10 (binary). After the timer has started counting down, the values residing in the count registers can be used to calculate the actual number of TIMER IN pulses required to complete the timer cycle if desired. To obtain the remaining count, the following operations should be done in order :

1. Stop the count.

2. Read in the 16-bit value from the count length registers.

3. Reset the upper two mode bits.

4. Reset the carry and rotate right one position all 16 bits through carry.

5. If carry is set, add 1/2 of the full original count ( $1/2$  full count $^{-1}$  if full count is odd.)

Note : When the initial count value is odd and the third count pulse has not come yet, it will be unknown whether one or two counts has occurred. Regardless of this, the TMP8155/8156 always counts out the right number of pulses in generating the **TIMEROUT** waveforms.

## 7. ELECTRICAL CHARACTERISTICS

### 7.1 ABSOLUTE MAXIMUM RATINGS

| Symbol              | Item                                                           | Rating         | Units |

|---------------------|----------------------------------------------------------------|----------------|-------|

| V <sub>CC</sub>     | V <sub>CC</sub> Supply Voltage with Respect to V <sub>SS</sub> | - 0.5 to + 7.0 | V     |

| P <sub>D</sub>      | Power Dissipation                                              | 1.5            | W     |

| T <sub>SOLDER</sub> | Soldering Temperature (Soldering Time 10 sec.)                 | 260            | °C    |

| T <sub>STG</sub>    | Storage Temperature                                            | - 55 to + 150  | °C    |

| T <sub>OPR</sub>    | Operating Temperature                                          | 0 to + 70      | °C    |

050489

### 7.2 D.C. CHARACTERISTICS

TA = 0°C to + 70°C, V<sub>CC</sub> = + 5V ± 5%

| Symbol               | Parameter                           | Test Conditions                            | Min.  | Max.                  | Units    |

|----------------------|-------------------------------------|--------------------------------------------|-------|-----------------------|----------|

| V <sub>IL</sub>      | Input Low Voltage                   |                                            | - 0.5 | 0.8                   | V        |

| V <sub>IH</sub>      | Input High Voltage                  |                                            | 2.0   | V <sub>CC</sub> + 0.5 | V        |

| V <sub>OL</sub>      | Output Low Voltage                  | I <sub>OL</sub> = 2mA                      | -     | 0.45                  | V        |

| V <sub>OH</sub>      | Output High Voltage                 | I <sub>OH</sub> = - 400μA                  | 2.4   | -                     | V        |

| I <sub>IL</sub>      | Input Leakage                       | V <sub>IN</sub> = V <sub>CC</sub> to 0V    | -     | ± 10                  | μA       |

| I <sub>LO</sub>      | Output Leakage Current              | 0.45V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> | -     | ± 10                  | μA       |

| I <sub>CC</sub>      | V <sub>CC</sub> Supply Current      |                                            | -     | 180                   | mA       |

| I <sub>IL</sub> (CE) | Chip Enable Leakage<br>8155<br>8156 | V <sub>IN</sub> = V <sub>CC</sub> to 0V.   | -     | + 100<br>- 100        | μA<br>μA |

050489

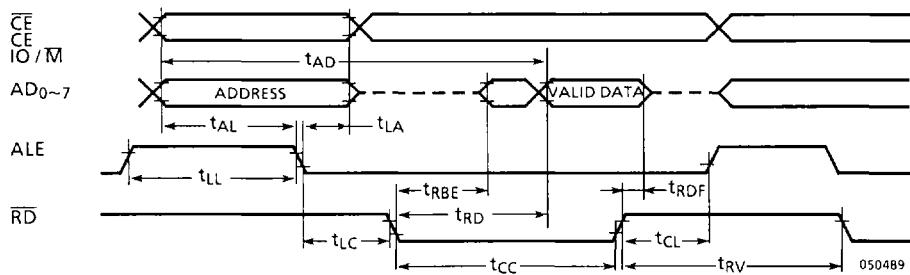

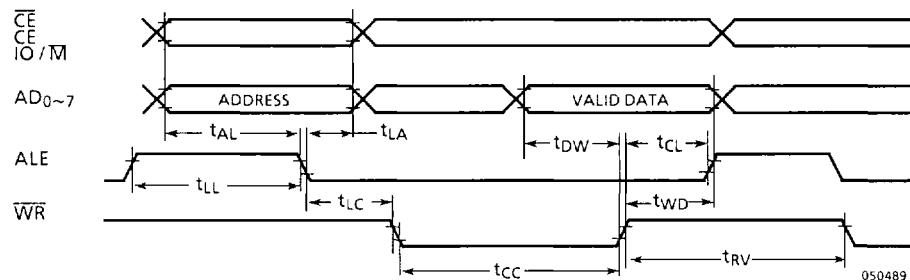

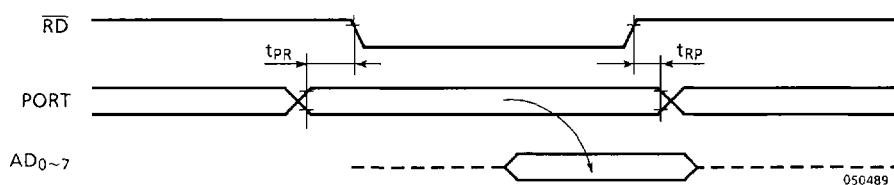

## 7.3 A.C. CHARACTERISTICS

TA = 0°C to + 70°C, V<sub>CC</sub> = + 5V ± 5%

| Symbol             | Parameters                                             | Min. | Max. | Units |

|--------------------|--------------------------------------------------------|------|------|-------|

| t <sub>AL</sub>    | Address to Latch Setup Time                            | 30   | —    | ns    |

| t <sub>LA</sub>    | Address Hold Time after Latch                          | 30   | —    | ns    |

| t <sub>LC</sub>    | Latch to READ / WRITE Control                          | 40   | —    | ns    |

| t <sub>RD</sub>    | Valid Data out Delay from READ Control                 | —    | 140  | ns    |

| t <sub>AD</sub>    | Address Stable To Data Out Valid                       | —    | 330  | ns    |

| t <sub>LL</sub>    | Latch Enable Width                                     | 70   | —    | ns    |

| t <sub>ROF</sub>   | Data Bus Float after READ                              | 0    | 80   | ns    |

| t <sub>CL</sub>    | READ / WRITE Control Latch Enable                      | 10   | —    | ns    |

| t <sub>CC</sub>    | READ / WRITE Control Width                             | 200  | —    | ns    |

| t <sub>DW</sub>    | Data in to WRITE Setup Time                            | 100  | —    | ns    |

| t <sub>WD</sub>    | Data in Hold Time After WRITE                          | 0    | —    | ns    |

| t <sub>RV</sub>    | Recovery Time Between Controls                         | 200  | —    | ns    |

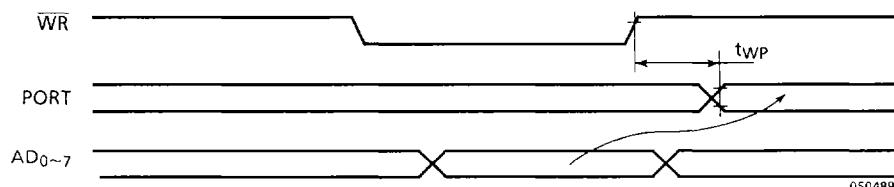

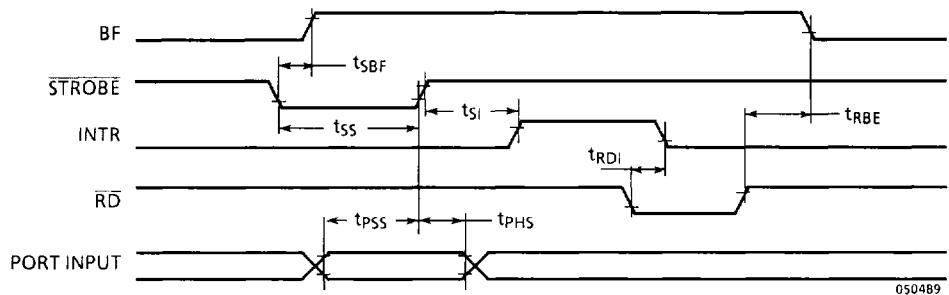

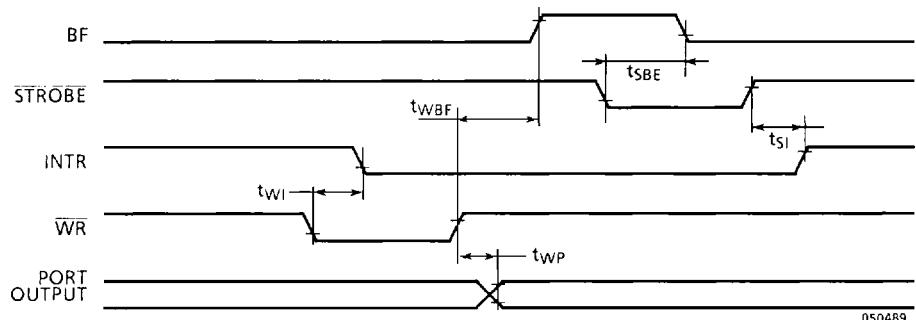

| t <sub>WP</sub>    | WRITE to Port Output                                   | —    | 300  | ns    |

| t <sub>PR</sub>    | Port Input Setup Time                                  | 50   | —    | ns    |

| t <sub>RP</sub>    | Port Input Hold Time                                   | 10   | —    | ns    |

| t <sub>SBF</sub>   | Strobe to Buffer Full                                  | —    | 300  | ns    |

| t <sub>SS</sub>    | Strobe Width                                           | 150  | —    | ns    |

| t <sub>RBE</sub>   | READ to Buffer Empty                                   | —    | 300  | ns    |

| t <sub>SI</sub>    | Strobe to INTR On                                      | —    | 300  | ns    |

| t <sub>ROI</sub>   | Strobe to INTR Off                                     | —    | 300  | ns    |

| t <sub>PS</sub>    | Port Setup Time to Strobe                              | 20   | —    | ns    |

| t <sub>PHS</sub>   | Port Hold Time after Strobe                            | 100  | —    | ns    |

| t <sub>SBE</sub>   | Strobe to Buffer Empty                                 | —    | 300  | ns    |

| t <sub>WBF</sub>   | WRITE to Buffer Full                                   | —    | 300  | ns    |

| t <sub>WI</sub>    | WRITE to INTR Off                                      | —    | 300  | ns    |

| t <sub>TL</sub>    | TIMER-IN to TIMEROUT Low                               | —    | 300  | ns    |

| t <sub>TH</sub>    | TIMER-IN to TIMEROUT High                              | —    | 300  | ns    |

| t <sub>RDE</sub>   | Data Bus Enable from READ Control                      | 10   | —    | ns    |

| t <sub>L</sub>     | TIMER-IN Low Time                                      | 40   | —    | ns    |

| t <sub>H</sub>     | TIMER-IN High Time                                     | 70   | —    | ns    |

| t <sub>CYC</sub>   | CLK Cycle Period                                       | 200  | —    | ns    |

| t <sub>r, tf</sub> | CLK Rise and Fall Time                                 | —    | 30   | ns    |

| t <sub>WT</sub>    | WRITE to TIMER-IN<br>(for writes which start counting) | 200  | —    | ns    |

230589

Notes : 1. Test conditions CL=150pF

2. Timing defining signal voltage are ;

Output High level = 2V, Low level = 0.8V

## 8. TIMING WAVEFORMS

Figure 8.1 READ CYCLE

Figure 8.2 WRITE CYCLE

Figure 8.3 BASIC INPUT MODE

Figure 8.4 BASIC OUTPUT MODE

Figure 8.5 STROBED INPUT MODE

Figure 8.6 STROBED OUTPUT MODE

Figure 8.7 TIMER OUTPUT WAVEFORM

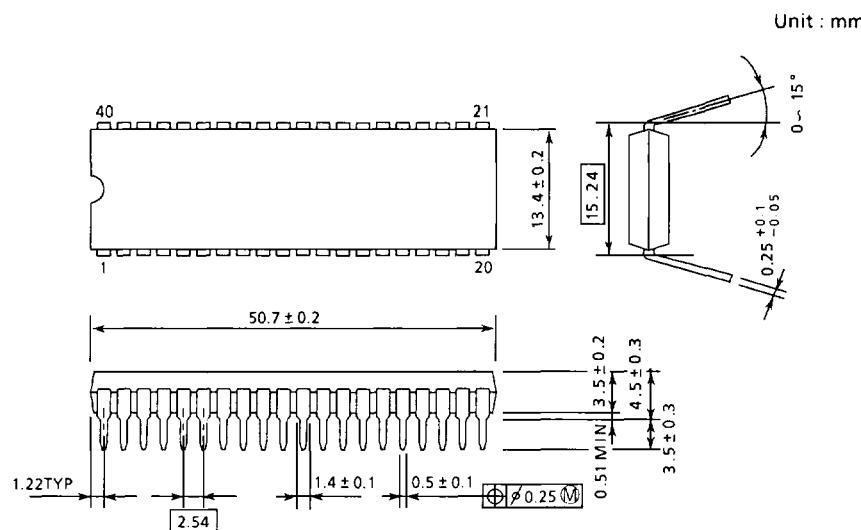

## 9. OUTLINE DRAWING (40Pins Plastic Package)

DIP40-P-600

270289

Note : Each lead pitch is 2.54mm, and all the leads are located within  $\pm 0.25$ mm from their theoretical positions with respect to No. 1 and No. 40 leads.