74LS138 is a member from ‘74xx’family of TTL logic gates. The chip is designed for decoding or de-multiplexing applications and comes with 3 3-input to 8-output setup. The design is also made for the chip to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems, these decoders can be used to minimize the effects of system decoding. The three enable pins of the chip (in Two active-low and one active-high) reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented with no external inverters, and a 32-line decoder requires only one inverter.

74LS138 is used in de-multiplexing applications by using the enable pin as the data input pin. Also, the chip inputs are clamped with high-performance Schottky diodes to suppress line-ringing and simplify system design.

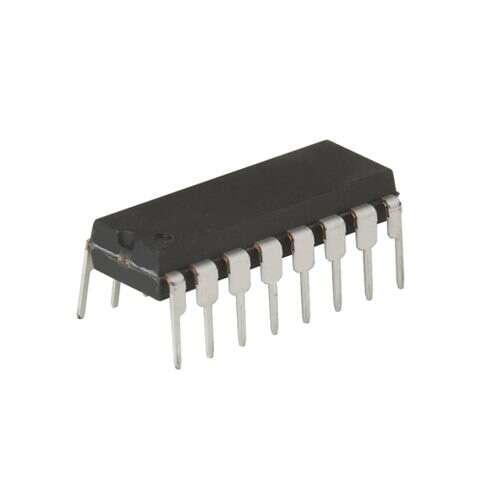

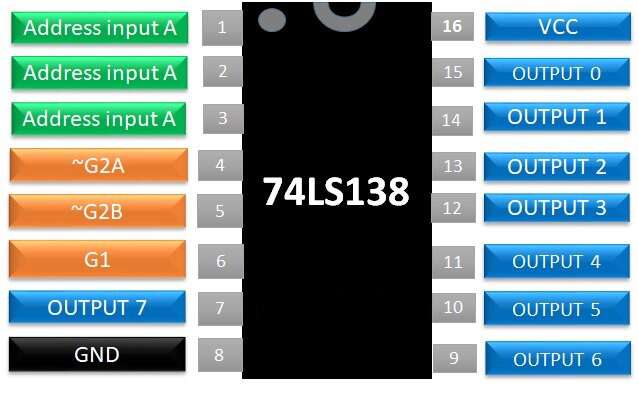

74LS138 Pin configuration

74LS138 is a sixteen-pin device as shown in the pin diagram and we will describe the function of each pin below.

| Pin | Name | Description |

| 1 | A | Address input pin |

| 2 | B | Address input pin |

| 3 | C | Address input pin |

| 4 | G2A | Enable input (active LOW) |

| 5 | G2B | Enable input (active LOW) |

| 6 | G1 | Enable input (active HIGH) |

| 7 | Y7 | Output pin 7 |

| 8 | GND | Ground |

| 9 | Y6 | Output pin 6 |

| 10 | Y5 | Output pin 5 |

| 11 | Y4 | Output pin 4 |

| 12 | Y3 | Output pin 3 |

| 13 | Y2 | Output pin 2 |

| 14 | Y1 | Output pin 1 |

| 15 | Y0 | Output pin 0 |

| 16 | VCC | Power supply pin |

Features and Electrical Characteristics of 74LS138 Decoder

| Physical | |

| Case/Package | PDIP |

| Contact Plating | Gold |

| Mount | Through Hole |

| Number of Pins | 16 |

| Technical | |

| Bandwidth | 35 MHz |

| High-Level Output Current | -400 µA |

| Independent Circuits | 1 |

| Input Current | 100 µA |

| Logic Function | Decoder, Demultiplexer |

| Low-Level Output Current | 8 mA |

| Max Operating Temperature | 70 °C |

| Max Power Dissipation | 1 mW |

| Max Supply Voltage | 5.25 V |

| Min Operating Temperature | 0 °C |

| Min Supply Voltage | 4.75 V |

| Number of Bits | 8 |

| Number of Channels | 1 |

| Number of Circuits | 1 |

| Number of Elements | 1 |

| Number of Input Lines | 3 |

| Number of Inputs | 3 |

| Number of Output Lines | 8 |

| Number of Outputs | 8 |

| Operating Supply Voltage | 5 V |

| Polarity | Inverting |

| Propagation Delay | 41 ns |

| Quiescent Current | 6.3 mA |

| Supply Type | Single |

| Turn-On Delay Time | 41 ns |

Overview of 74LS138 Decoder

As mentioned earlier the chip is specifically designed to be used in high-performance memory-decoding or data-routing applications which require very short propagation delay times. The memory unit data exchange rate determines the performance of any application and the delays of any kind are not tolerable there. In such applications using a 74LS138 line decoder is ideal because the delay times of this device are less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible to affect the performance.

How to use 74LS138 Decoder

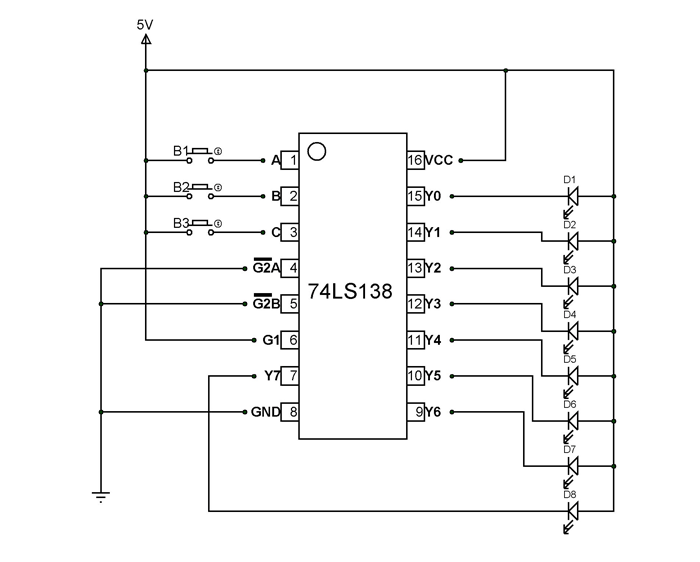

To understand the working of the device let us construct a simple application circuit with a few external components as shown below.

About the circuit: Here the outputs are connected to LED to show which output pin goes LOW and do remember the outputs of the device are inverted. We are using a single device so we will connect the G2A and G2B pins to the ground followed by connecting G1 to VCC to enable the chip. The three buttons here represent three input lines for the device.

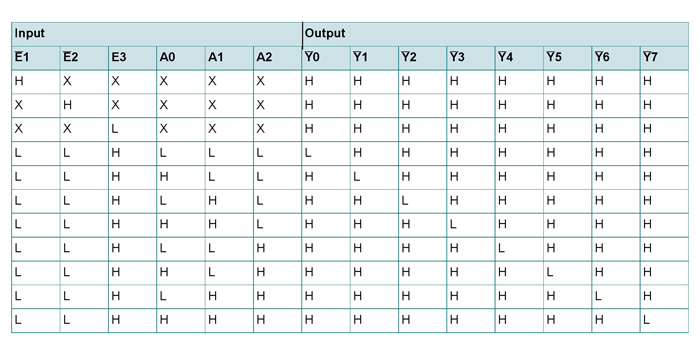

For understanding the working let us consider the truth table of the device.

H = HIGH, L = LOW and X = Don’t Care

Working of circuit

As shown in table first three rows the enable pins needed to be connected appropriately or irrespective of input lines all outputs will be high. After connecting the enable pins as shown in the circuit diagram you can use the input line to get the output.

After powering, if all buttons are not pressed Y0 will be LOW, and the remaining output will be HIGH as shown in the table. After only B1 is pressed, A0=HIGH and Y1 will become LOW while the remaining will be HIGH. Following if only B2 is pressed, A1=HIGH and Y2 will become LOW while remaining will be HIGH. This way we can realize all the truth tables by toggling the three buttons B1, B2, and B3 (Three inputs A0, A1, and A2), and with that we have three input to eight output decoders.

Applications

- Line decoders

- Servers

- Digital systems

- Line De-multiplexing

- Telecom circuits

- Memory circuits