Features

![]() Two J-K Master/Slave Flip Flops in a 14-Pin DIP Package

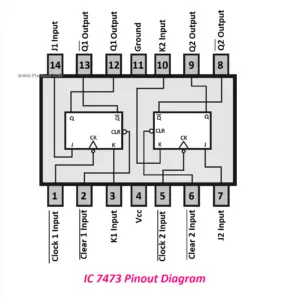

Two J-K Master/Slave Flip Flops in a 14-Pin DIP Package

![]() Outputs Directly Interface to CMOS, NMOS and TTL

Outputs Directly Interface to CMOS, NMOS and TTL

![]() Large Operating Voltage Range

Large Operating Voltage Range

![]() Wide Operating Conditions

Wide Operating Conditions

Technical Specifications

| Physical | |

| Case/Package | PDIP |

| Contact Plating | Gold |

| Mount | Through Hole |

| Number of Pins | 14 |

| Technical | |

| Clock Edge Trigger Type | Negative Edge |

| Frequency | 60 MHz |

| High Level Output Current | -4 mA |

| Logic Function | Flip-Flop, JK-Type |

| Low Level Output Current | 4 mA |

| Max Frequency | 20 MHz |

| Max Operating Temperature | 125 °C |

| Max Supply Voltage | 5.5 V |

| Min Operating Temperature | -55 °C |

| Min Supply Voltage | 4.5 V |

| Number of Bits | 2 |

| Number of Bits per Element | 1 |

| Number of Channels | 2 |

| Number of Circuits | 2 |

| Number of Elements | 2 |

| Number of Input Lines | 2 |

| Number of Output Lines | 1 |

| Operating Supply Voltage | 5 V |

| Output Current | 4 mA |

| Polarity | Non-Inverting |

| Propagation Delay | 38 ns |

| Quiescent Current | 4 µA |

| Turn-On Delay Time | 38 ns |

Datasheet

Reviews

There are no reviews yet.