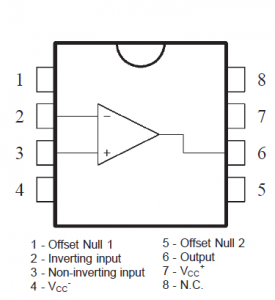

Layout Pin:

LF357 Pin Configuration

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | BALANCE PIN 1 | Offset Balancing Pin 1 |

| 2 | IN 1 | Input Pin 1 |

| 3 | IN 2 | Input Pin 2 |

| 4 | V- | Negative Power Supply |

| 5 | BALANCE PIN 1 | Offset Balancing Pin 2 |

| 6 | OUTPUT | Output Pin |

| 7 | V+ | Positive Power Supply |

| 8 | NC | No Connection |

Specifications:

| Product Attribute | Attribute Value |

| Product Category: | Operational Amplifiers – Op Amps |

| Number of Channels: | 1 Channel |

| GBP – Gain Bandwidth Product: | 20 MHz |

| SR – Slew Rate: | 50 V/us |

| Vos – Input Offset Voltage: | 10 mV |

| Ib – Input Bias Current: | 200 pA |

| Supply Voltage – Max: | 22 V |

| Supply Voltage – Min: | – 22 V |

| Operating Supply Current: | 10 mA |

| CMRR – Common Mode Rejection Ratio: | 80 dB |

| en – Input Voltage Noise Density: | 15 nV/sqrt Hz |

| Package/Case: | PDIP-8 |

| Mounting Style: | Through Hole |

| Minimum Operating Temperature: | 0 C |

| Maximum Operating Temperature: | + 70 C |

| Series: | LF357 |

| Maximum Dual Supply Voltage: | +/- 18 V |

| Operating Supply Voltage: | +/- 18 V |

| Pd – Power Dissipation: | 670 mW |

| Product: | Operational Amplifiers |

| Subcategory: | Amplifier ICs |

| Supply Type: | Dual |

Reviews

There are no reviews yet.